Cadence楷登電子近日正式揭曉了其最新研發(fā)成果——Tensilica NeuroEdge 130 AI協(xié)處理器(AICP)。這一創(chuàng)新產(chǎn)品于5月7日面向全球發(fā)布,標(biāo)志著Cadence在AI處理器領(lǐng)域邁出了重要一步。

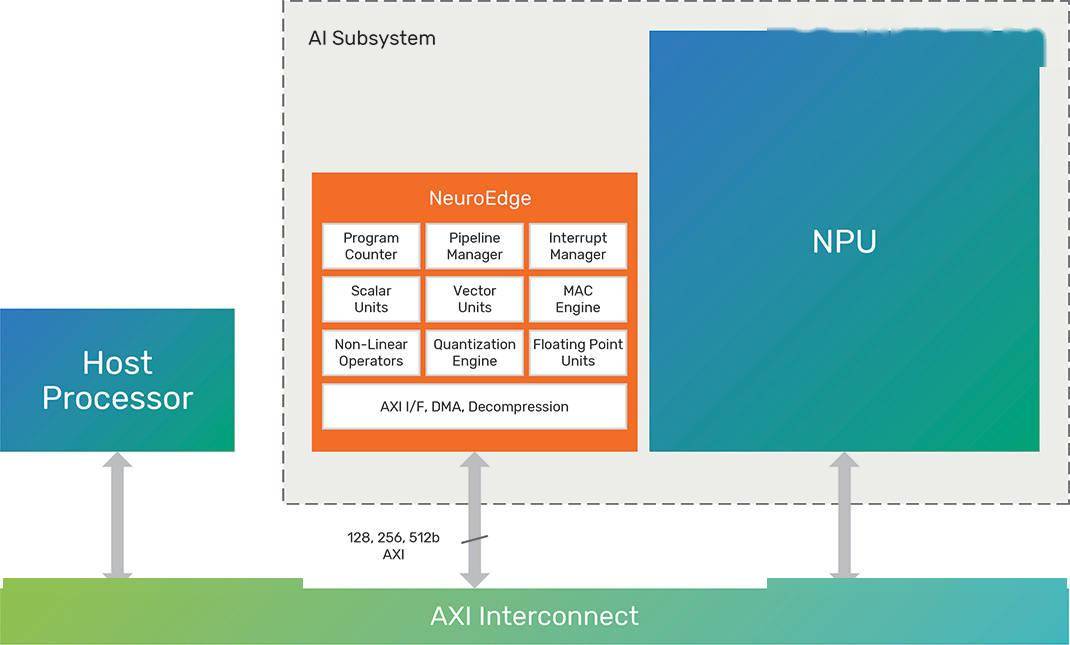

Tensilica NeuroEdge 130 AICP建立在Cadence久經(jīng)考驗的Tensilica Vision系列DSP IP基礎(chǔ)之上,采用先進的VLIW(Very Long Instruction Word)基SIMD(單指令多數(shù)據(jù))架構(gòu)。該架構(gòu)不僅大幅提升了性能,還在保持軟件兼容性的同時,實現(xiàn)了面積和功耗的雙重優(yōu)化。與原版本相比,它在同等性能下節(jié)省了超過30%的面積和超過20%的動態(tài)功耗,從而加速了芯片方案的商業(yè)化進程。

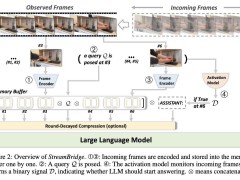

在實際部署中,Tensilica NeuroEdge 130 AICP能夠協(xié)同NPU(神經(jīng)網(wǎng)絡(luò)處理器)工作,負責(zé)處理一系列NPU未專門優(yōu)化的任務(wù),如預(yù)處理和后處理。這一特性使得AI子系統(tǒng)在可編程性、靈活性和前瞻性方面得到了顯著提升。AICP能夠向NPU發(fā)出指令和命令,從而優(yōu)化整體AI工作流程,提高整體效率。

Cadence高級副總裁兼硅解決方案集團總經(jīng)理Boyd Phelps對此表示:“我們利用Tensilica DSP的成功經(jīng)驗,驗證了AICP的廣闊應(yīng)用前景。隨著AI工作負載的不斷演變和領(lǐng)域?qū)S眯缘闹饾u降低,我們的AI SoC和系統(tǒng)客戶對小型、高效的AICP需求日益迫切,以獲取更優(yōu)的PPA(性能、功耗、面積)和未來性能。”

為了繼續(xù)保持其在IP創(chuàng)新領(lǐng)域的領(lǐng)先地位,Cadence推出了這款專為NPU配套設(shè)計的新型處理器。Tensilica NeuroEdge 130 AICP不僅滿足了客戶對最苛刻AI應(yīng)用的需求,還樹立了性能效率的新標(biāo)桿。

通過引入Tensilica NeuroEdge 130 AICP,Cadence進一步鞏固了其在AI處理器市場的領(lǐng)先地位,并為未來的AI技術(shù)發(fā)展奠定了堅實基礎(chǔ)。這一創(chuàng)新成果不僅展現(xiàn)了Cadence在技術(shù)研發(fā)方面的強大實力,還預(yù)示著AI技術(shù)在更廣泛領(lǐng)域的應(yīng)用前景。